- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

Epitaxieschichten: Die Grundlage fortschrittlicher Halbleiterbauelemente

Abbildung 1: Veranschaulicht den Zusammenhang zwischen Dotierungskonzentrationen, Schichtdicke und Durchbruchspannung für unipolare Geräte.

Die Herstellung von SiC-Epitaxieschichten umfasst hauptsächlich Techniken wie Verdampfungswachstum, Flüssigphasenepitaxie (LPE), Molekularstrahlepitaxie (MBE) und chemische Gasphasenabscheidung (CVD), wobei CVD die vorherrschende Methode für die Massenproduktion in Fabriken ist.

Tabelle 1: Bietet einen vergleichenden Überblick über die wichtigsten Methoden zur Herstellung epitaktischer Schichten.

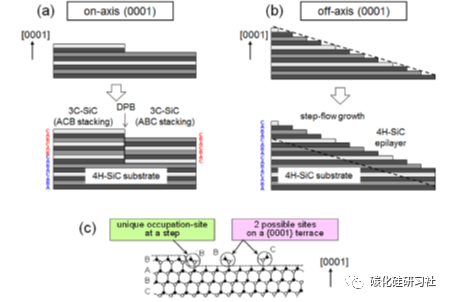

Ein bahnbrechender Ansatz beinhaltet das Wachstum auf außeraxialen {0001}-Substraten in einem bestimmten Neigungswinkel, wie in Abbildung 2(b) dargestellt. Diese Methode erhöht die Stufendichte erheblich und reduziert gleichzeitig die Stufengröße. Dadurch wird die Keimbildung vor allem an den Stellen der Stufenbündelung erleichtert. Dadurch kann die Epitaxieschicht die Stapelsequenz des Substrats perfekt nachbilden und die Koexistenz von Polytypen verhindern.

Abbildung 2: Demonstriert den physikalischen Prozess der stufengesteuerten Epitaxie in 4H-SiC.

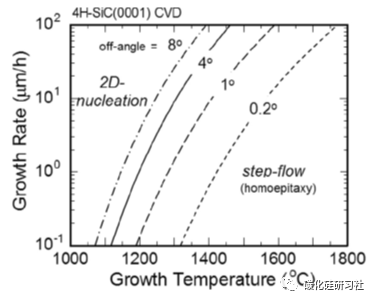

Abbildung 3: Zeigt die kritischen Bedingungen für das CVD-Wachstum bei der stufengesteuerten Epitaxie für 4H-SiC.

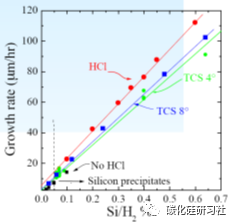

Abbildung 4: Vergleich der Wachstumsraten unter verschiedenen Siliziumquellen für die 4H-SiC-Epitaxie.

Im Bereich der Nieder- und Mittelspannungsanwendungen (z. B. 1200-V-Geräte) hat die SiC-Epitaxietechnologie ein ausgereiftes Stadium erreicht und bietet eine relativ überlegene Gleichmäßigkeit in Dicke, Dotierungskonzentration und Defektverteilung und erfüllt damit die Anforderungen für Nieder- und Mittelspannungs-SBD angemessen , MOS, JBS-Geräte und andere.

Der Hochspannungsbereich stellt jedoch immer noch erhebliche Herausforderungen dar. Beispielsweise erfordern Geräte mit einer Nennspannung von 10.000 V epitaktische Schichten mit einer Dicke von etwa 100 μm, aber diese Schichten weisen im Vergleich zu ihren Niederspannungsgegenstücken eine erheblich geringere Dicke und Gleichmäßigkeit der Dotierung auf, ganz zu schweigen von den nachteiligen Auswirkungen dreieckiger Defekte auf die Gesamtleistung des Geräts. Hochspannungsanwendungen, die tendenziell bipolare Geräte bevorzugen, stellen auch strenge Anforderungen an die Lebensdauer der Minoritätsträger, was eine Prozessoptimierung zur Verbesserung dieses Parameters erforderlich macht.

Derzeit wird der Markt von 4-Zoll- und 6-Zoll-SiC-Epitaxiewafern dominiert, wobei der Anteil von SiC-Epitaxiewafern mit großem Durchmesser allmählich zunimmt. Die Größe von SiC-Epitaxiewafern wird im Wesentlichen durch die Abmessungen der SiC-Substrate bestimmt. Da 6-Zoll-SiC-Substrate mittlerweile im Handel erhältlich sind, schreitet der Übergang von der 4-Zoll- zur 6-Zoll-SiC-Epitaxie stetig voran.

Mit der Weiterentwicklung der Technologie zur Herstellung von SiC-Substraten und der Erweiterung der Produktionskapazitäten sinken die Kosten für SiC-Substrate zunehmend. Angesichts der Tatsache, dass Substrate mehr als 50 % der Kosten epitaktischer Wafer ausmachen, werden die sinkenden Substratpreise voraussichtlich zu niedrigeren Kosten für die SiC-Epitaxie führen und damit eine bessere Zukunft für die Branche versprechen.**